The choice for the design based on complementary metal–oxide semiconductors arise from its numerous advantages in logic family applications. CMOS offers straightforward driving facilitated by the gate oxide, a robust fan-out capability, and high input impedance. Its benefits extend to near rail-to-rail swing due to the complementary pair structure and low static power consumption.

CMOS design offers compatibility with memory devices and high device density. Beyond digital design, complementary devices enhance various circuits, such as those employing active-load architectures or exploiting flexibility to switch on either the low side or the high side. When faced with limitations, circuit designers adapt, as seen in the adoption of direct-coupled FET logic in instances where pMOS is unavailable but both depletion-mode and enhancement nMOS devices are integrated, as observed in various Gallium Nitride processes.

It is also important to know the scope of the device based on its configuration and how it is placed. Traditionally, vertical devices have subdued the high density and power silicon market as they could have contact with both the bottom and upper layers of the epitaxial layers.

On the other hand, when achieving close integration of power devices and controls it is of utmost importance to minimize connection parasitic for high operating frequencies, therefore lateral devices emerge as the preferred choice, particularly within the control circuitry. This preference arises due to their seamless compatibility with standard integrated circuit layouts. On-chip interconnects prove to be superior in terms of performance and reliability compared to configurations involving bumps, traces, wire bonds, fusing material, and other elements that would otherwise compose a complete system from standalone parts. This on-chip integration not only enhances reliability but also boosts performance, enabling operation at higher frequencies. Consequently, it facilitates the reduction in the size of large reactive elements.

Exploring new and Improved Wide Bandgap and Ultrawide Bandgap Materials for CMOS Devices

The selection of materials in the manufacturing of CMOS devices significantly influences their performance and capabilities. Silicon has long been the foundation of CMOS devices, offering scalability and reliability, but the integration of wide bandgap materials like Silicon Carbide and Gallium Nitride has escorted in improvements in breakdown voltages and switching speeds. Lateral devices, particularly in power and control integration, present advantages in compatibility and reduced parasitic at high frequencies.

The quest for innovation and discovery of new and improved materials extends to ultrawide bandgap materials like diamond, holding promise for advanced CMOS devices with exceptional thermal conductivity. Understanding the impact of diverse materials is crucial in exploiting the dynamic landscape of CMOS manufacturing, paving the way for more efficient and high-performance electronic devices. The most suited and talked about material for CMOS devices is Silicon Carbide as it already has an established platform with extreme condition studies and complex digital circuit designs.

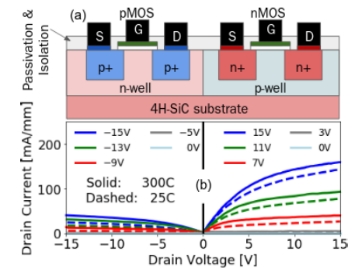

One of the most striking features of Silicon Carbide is its extensive temperature operating range, which is between 200◦C to 300◦C for high-temperature silicon-on-insulator, that is used in NASA’s JFET circuits, and it is capable of handling extremely harsh space conditions. On the other hand, SiC MOS devices are facing significantly tougher barriers like high interface trap density and low inversion-channel mobility. In order to tackle this issue, the state-of-the-art 1.2-μm HiTSiC process designed by Raytheon as shown in Figure 1 is the Industrial standard that employs two separate doped p and n wells in order to seamlessly work at 15 V.

+86 15756287732

+86 15756287732